Feature Story

More feature stories by year:

2024

2023

2022

2021

2020

2019

2018

2017

2016

2015

2014

2013

2012

2011

2010

2009

2008

2007

2006

2005

2004

2003

2002

2001

2000

1999

1998

![]() Return to: 2014 Feature Stories

Return to: 2014 Feature Stories

CLIENT: IMAGINATION TECHNOLOGIES

Sept. 3, 2014: ExtremeTech

When Imagination Technologies bought MIPS in 2011, it was clearly aiming to create a new portfolio of CPU products that could challenge companies like ARM across multiple business segments. The move surprised a number of people — ARM's success and ascension seemed to be unstoppable, particularly for a player like MIPS. While it was once the architecture that many of the world's supercomputers and high-end workstations ran on, big design wins languished and MIPS gradually became a player in embedded markets and other low-visibility systems.

When Imagination Technologies bought MIPS in 2011, it was clearly aiming to create a new portfolio of CPU products that could challenge companies like ARM across multiple business segments. The move surprised a number of people — ARM's success and ascension seemed to be unstoppable, particularly for a player like MIPS. While it was once the architecture that many of the world's supercomputers and high-end workstations ran on, big design wins languished and MIPS gradually became a player in embedded markets and other low-visibility systems.

Bit by bit, Imagination Technologies has been working to change that, rolling out a series of cores with higher throughput, advanced capabilities, and better overall performance. Today's unveil of the Warrior I6400 is the latest effort, and while it's not MIPS's fastest CPU for single-threaded performance, its multithreaded capabilities, CMT, and cluster options make it, in some ways, the most advanced part MIPS currently fields.

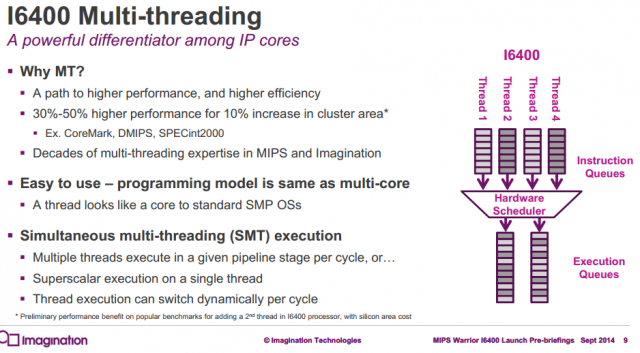

The new I6400 drops into the mid-range, with an estimated 2.3-3.0 DMIPS per MHz (a common measure of embedded performance). The full-sized "P-class" core has a performance rate as high as 3.5 DMIPS/MHz. The new I6400 will use the MIPS64 instruction set (Release 6) — but is also designed to implement multithreading within the core, as shown below:

This diagram will be familiar to anyone who has ever looked at a model of Intel's Hyper-Threading (or simultaneous multithreading in general). Instructions fed from four separate threads are being scheduled and executed in two separate execution queues. This approach allows for what Imagination Technologies claims is a 30-50% improvement in performance for just 10% additional die space.

Simultaneous multithreading is optional in the I6400′s design — Imagination expects to see some customers opt for it while others won't be interested — but it's an excellent way to improve die utilization and overall efficiency. It's the reason why the company estimates a performance range of 2.3 – 3 DMIPS/MHz.

The system can execute multiple threads in a given pipeline stage or operate in superscalar mode (meaning it dispatches multiple instructions within the same thread to different execution units across the processor.

So, just how powerful is the CPU core itself? Let's take a look.

Architecturally, the I6400 bears a fair of similarity to the Cortex-A53 — a dual-issue, in-order core that can support between 1 and 4 threads with a wide array (for a low-power core) of execution units.

Interestingly, the integer pipelines can perform what Imagination calls instruction bonding. If two sequential integer operations arrive one right after the other, the I6400 can combine them into a single instruction. Two 32-bit integer operations become one 64-bit operation, two 64-bit operations can be combined into a single 128-bit access. Since the load/store unit is already 128 bits wide to accommodate the core's SIMD units, this bonding mechanism can boost performance over relying on just a single load/store unit, while saving power and die area.

The cluster architecture is also interesting.

See the bit on the right side of the block — ACE/AXI4? MIPS is using ARM's own interconnect standard for tying multiple clusters together — a bit of irony, considering the company wants to compete with ARM. Each cluster can be outfitted with an L2 cache of varying size from 512KB to 8MB and the clusters support DVFS (Dynamic Voltage and Frequency Scaling). Rather than relying on snoop filters to maintain cache coherence — this is a system where every core monitors the contents of every other core's caches — the I6400 relies on directory coherence. Directory coherence means that a section of the L2 is used to maintain a directory of what data is stored where — this drastically reduces bandwidth and power requirements.

MIPS wouldn't name names when we asked for companies that are interested in evaluating the processor, but it pointed out that the I6400′s clustering capabilities and scaling are of great interest to companies in both the mobile and HPC space. China licenses the MIPS architecture for its supercomputer and homegrown processor efforts – we covered the MIPS ISA efficiency of the Loongson processor family in our recent ISA discussion. Once upon a time, MIPS was the public face of the entire RISC architecture movement and powered some of the most impressive computers of its day — it's not impossible to think it could do so again, particularly if Imagination continues investing in the project.

Consumers, however, are likely to encounter MIPS in the low-cost tablet market where the architecture has already seen some limited adoption. Google has historically supported MIPS with Android, but the overwhelming majority of apps don't natively support it on that platform.

There are two reasons to think Imagination Technologies might be able to mount a successful challenge at the low end of the market. First, the company has a robust and widely licensed set of GPU IP that it could potentially use to sweeten the deal with prospective licensees. ARM, of course, has its own Mali architecture, but PowerVR remains one of the largest GPU vendors by market share.

Second, we've already seen multiple manufacturers vying for space in entry-level markets. Just as Rockchip and MediaTek have emerged to challenge Qualcomm, other companies could emerge to challenge them — and MIPS might be useful as a means of differentiation.

Return to: 2014 Feature Stories